The DE25-Nano FPGA development board brings a major step forward in embedded system design by combining reconfigurable hardware with strong processing power. Developed by Terasic, this compact board integrates Intel’s Agilex 5 FPGA alongside a dual-cluster ARM Cortex-A76/A55 hard processor system (HPS), making it well-suited for AI, robotics, and real-time signal processing.

Following the success of the DE10-Nano, the DE25-Nano improves performance and flexibility while keeping the same compact size. Its design supports both hardware acceleration and software execution, giving developers a reliable platform for building efficient and scalable solutions to handle complex tasks.

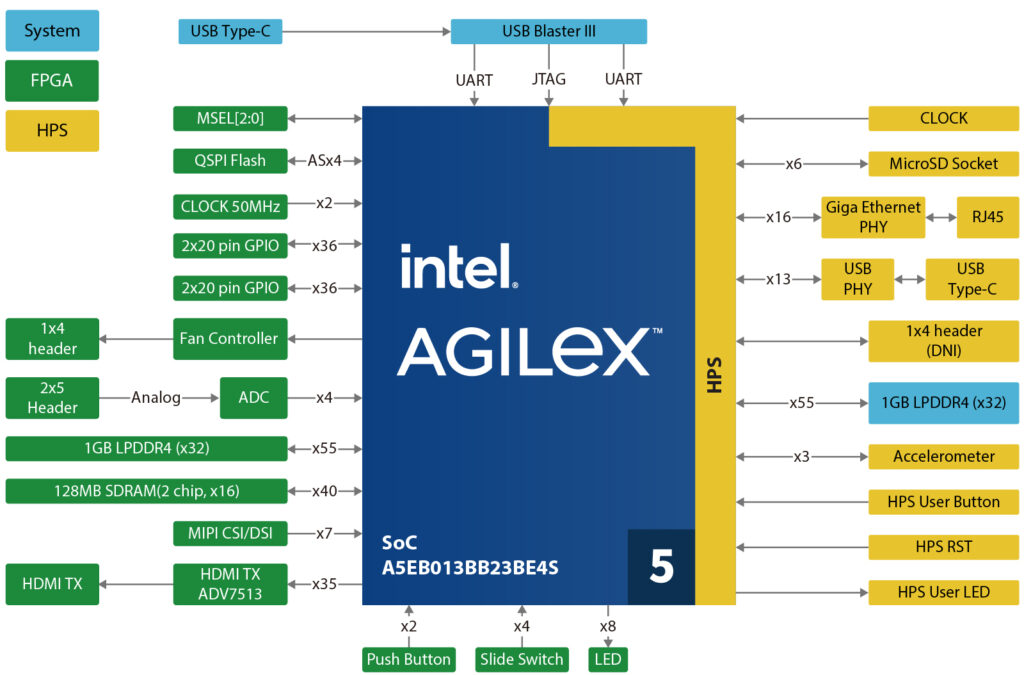

Intel’s Agilex 5 FPGA Block Diagram

DE25-Nano Development and Education Board Specifications:

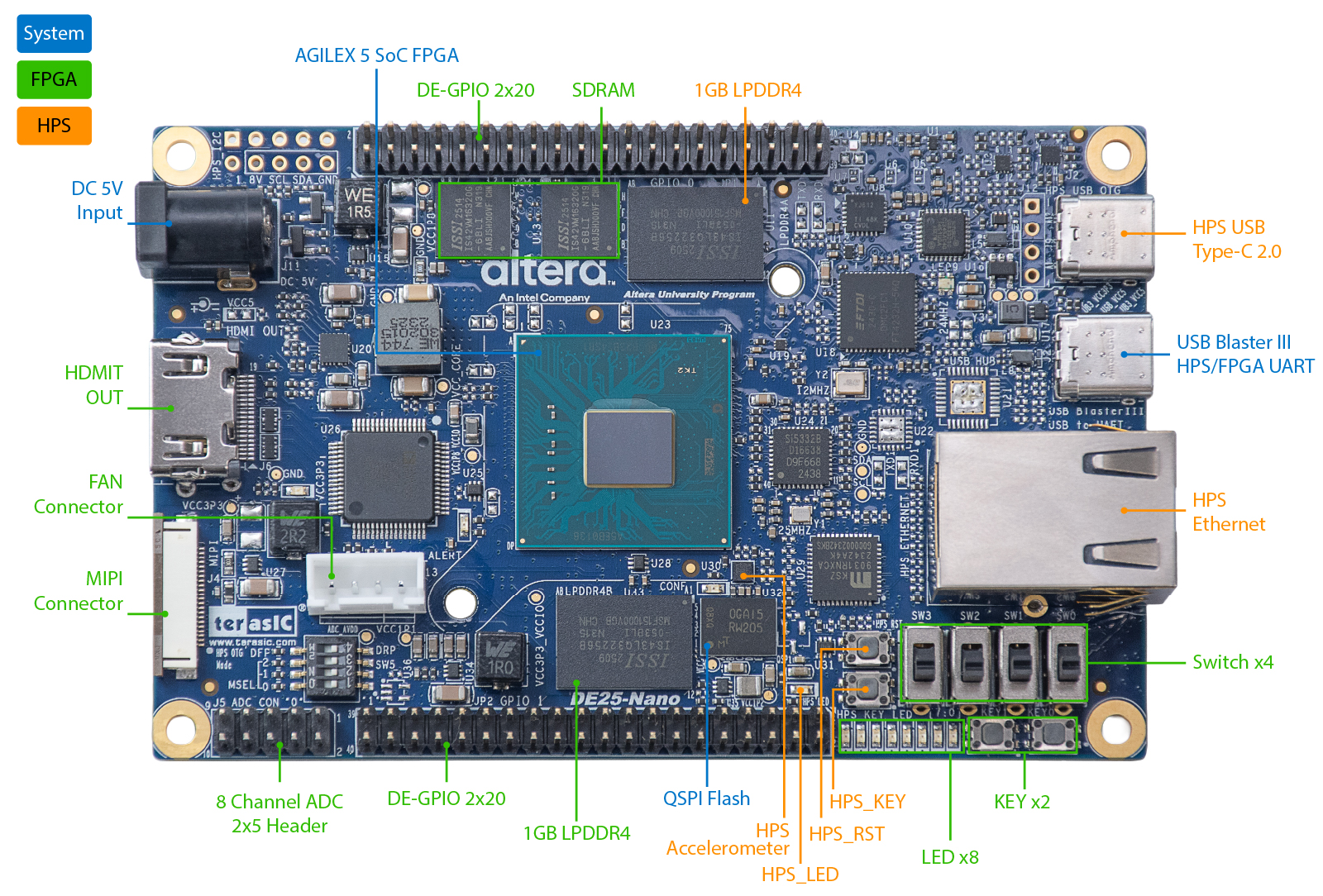

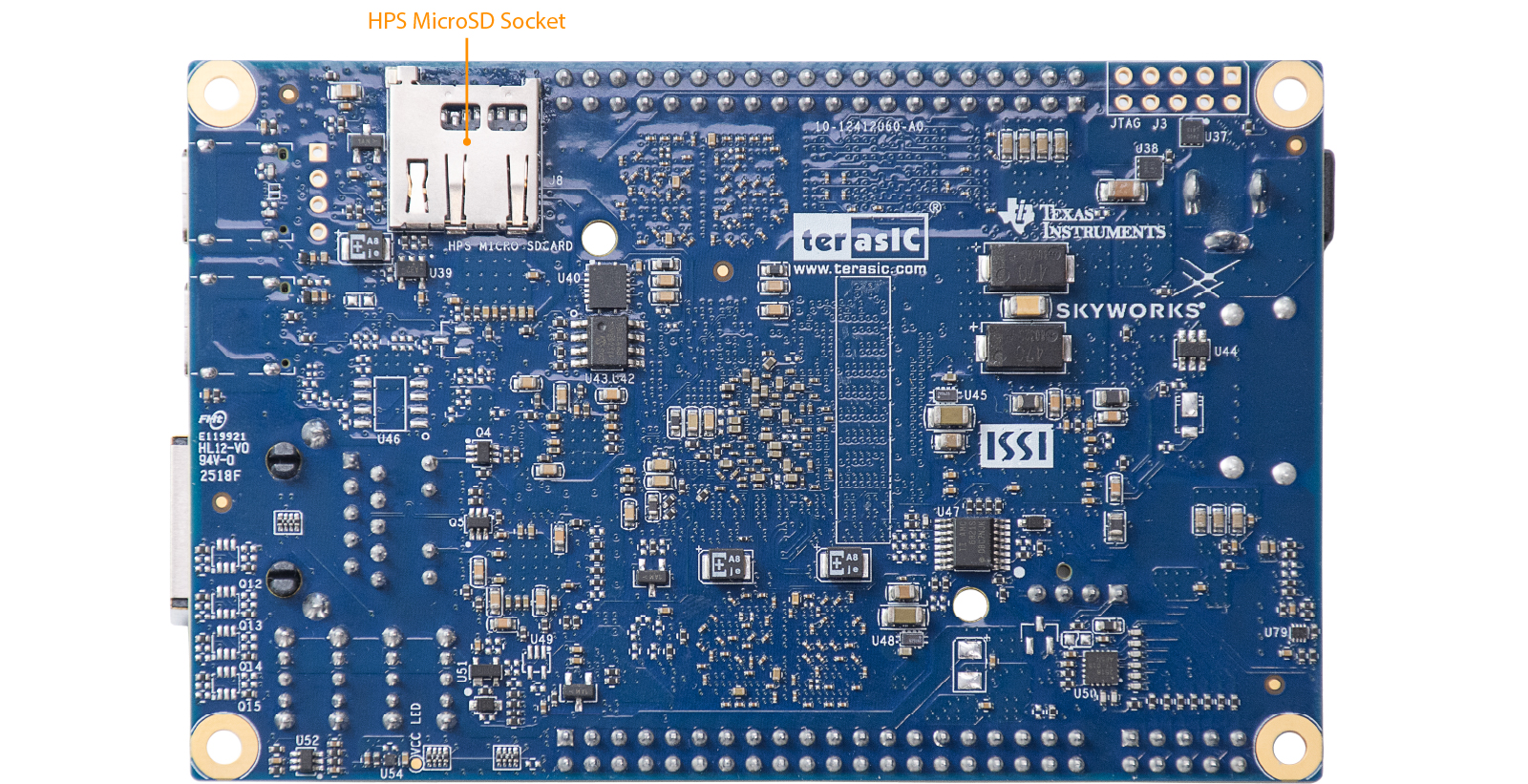

The DE25-Nano FPGA development board is powered by an Intel Agilex 5 A5EB013BB23BE4SR1 FPGA with 138K logic elements and integrates a dual-cluster ARM Cortex-A76/A55 hard processor system (HPS). It includes 1GB of LPDDR4 memory (shared between FPGA and HPS) with a data rate of 2133 MT/s and an additional 128MB SDRAM. The board measures 106.9mm x 68.58mm and comes with an onboard USB-Blaster III programmer through a USB Type-C connector, supporting ASx4 configuration with a 128Mbit QSPI Flash device.

DE25 NANO FPGA development board Front Side Specifications

For I/O and expansion, the DE25-Nano offers Gigabit Ethernet, USB 2.0 via Type-C, UART, and a MicroSD socket for boot and storage. It supports HDMI 2.0 output up to 1080p resolution and includes a MIPI connector with two data lanes for camera input. Developers also benefit from an 8-channel, 12-bit ADC, two 40-pin GPIO headers, a 10-pin analog header, and a range of user interfaces, including LEDs, buttons, and slide switches. The board integrates sensors such as an accelerometer and a temperature sensor, along with a fan controller for active cooling.

On the HPS side, the board extends functionality with dedicated LEDs, buttons, and a cold reset button. It supports Linux BSP, FPGA example projects, and seamless integration with Intel Quartus Pro software. With its mix of high-performance FPGA logic, ARM-based processing, and versatile connectivity, the DE25-Nano serves as a compact yet powerful platform for embedded AI, vision, and real-time processing applications.

DE25 NANO FPGA development board Back Side Specifications

The DE25-Nano development board comes with strong software support to simplify project development. Terasic provides a complete board support package (BSP) that includes Linux-based examples and FPGA design templates. Developers can integrate the board with Intel’s Quartus Pro design software for efficient hardware design and debugging, making it easier to unlock the full potential of both the FPGA and HPS. This software ecosystem helps streamline the development process for advanced and complex applications.

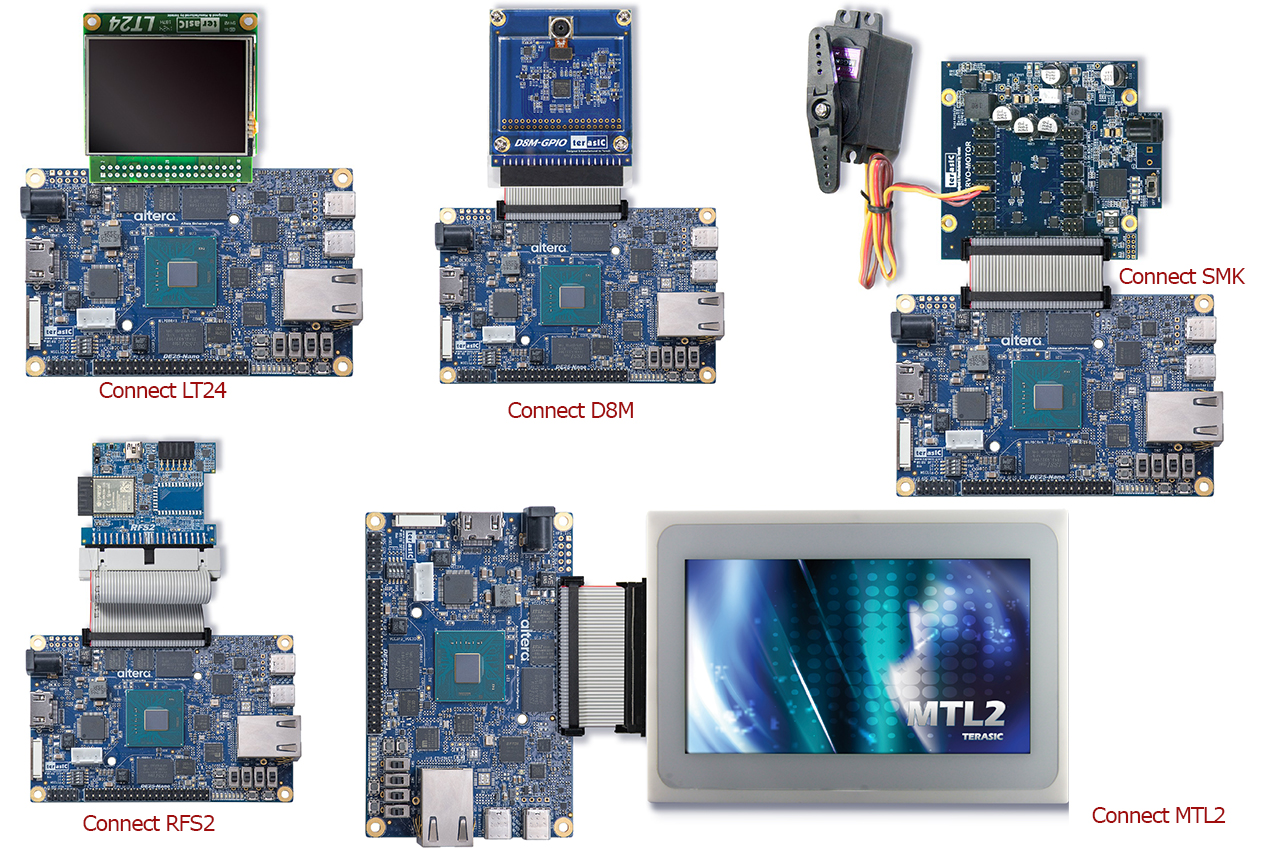

In addition to software, the DE25-Nano supports connectivity with various expansion modules, including the 2×20 GPIO Daughter Card, LT24 display, MTL2 touchscreen, D8M camera, SMK sensor kit, and RFS2 RF module. These add-ons extend the board’s flexibility, allowing developers to tailor the platform for applications in vision, sensing, wireless communication, and user interface design.

The DE25-Nano FPGA development board can be purchased directly from Terasic’s official website. The standard edition is priced at $248, while an academic version is available at a discounted price of $207. Developers can also add an optional USB WiFi dongle for $8. More details and ordering options can be found on the Terasic DE25-Nano product page.